Intel ra mắt mô-đun quang học mesh-to-mesh đầu tiên tại hội nghị chip Hot Chips 2023, cho thấy sự tiến bộ của họ trong tương lai của các kết nối chip-to-chip quang học cũng được các công ty như Nvidia và Ayar Labs ủng hộ. Tuy nhiên, chip 8 lõi 528 luồng mà Intel sử dụng cho bài trình diễn đã chiếm spotlight do kiến trúc độc đáo của nó với 66 luồng mỗi lõi để cho phép truyền dữ liệu lên đến 1TB/s. Đáng ngạc nhiên, chip chỉ tiêu thụ 75W điện, với ~60% điện năng được sử dụng bởi các kết nối quang học, nhưng thiết kế cuối cùng có thể cho phép các hệ thống với hai triệu lõi được kết nối trực tiếp với độ trễ dưới 400ns.

Chip PUMA (Programmable Unified Memory Architecture - Kiến trúc bộ nhớ hợp nhất có thể lập trình) của Intel là một phần của chương trình DARPA HIVE tập trung vào việc cải thiện hiệu suất trong công việc phân tích đồ thị quy mô petabyte để giải phóng 1000 lần cải thiện hiệu suất trên mỗi watt trong các tác vụ thưa thớt.

Đáng ngạc nhiên đối với một công ty tập trung vào x86 như Intel, chip thử nghiệm sử dụng kiến trúc RISC tùy chỉnh để mang lại hiệu suất tối ưu trong các tác vụ phân tích đồ thị, mang lại 8 lần cải thiện hiệu suất đơn luồng. Chip cũng được tạo ra bằng quy trình 7nm của TSMC, không phải các nút nội bộ của Intel.

Sau khi mô tả các tác vụ mục tiêu, Intel kết luận rằng họ cần tạo ra một kiến trúc giải quyết các thách thức liên quan đến stress cực độ đối với hệ thống bộ nhớ, các đường ống sâu, bộ dự đoán nhánh và logic không theo thứ tự do tác vụ tạo ra.

Core tùy chỉnh của Intel sử dụng cực kỳ song song với 66 luồng phần cứng cho mỗi lõi tám, bộ nhớ cache chỉ lệnh và dữ liệu L1 lớn và 4MB SRAM scratchpad mỗi lõi. Chip tám lõi có 32 cổng I/O quang hoạt động ở 32 GB/s/dir, tổng cộng 1TB/s tổng băng thông. Các chip thả vào giá đỡ máy chủ OCP tám socket, cung cấp tổng thông lượng quang học 16 TB/s cho hệ thống và mỗi chip được cấp nguồn bởi 32GB DDR5-4000 DRAM tùy chỉnh.

Intel đã sản xuất chip trên quy trình 7nm của TSMC với 27,6 tỷ transistor trải rộng trên die 316mm^2. Tám lõi, chiếm 1,2 tỷ transistor, chạy dọc theo trung tâm của die, được bao flank bởi tám bộ điều khiển bộ nhớ tùy chỉnh với độ phân giải truy cập 8 byte. Các router giao tiếp chiếm trung tâm 'trống' của chip.

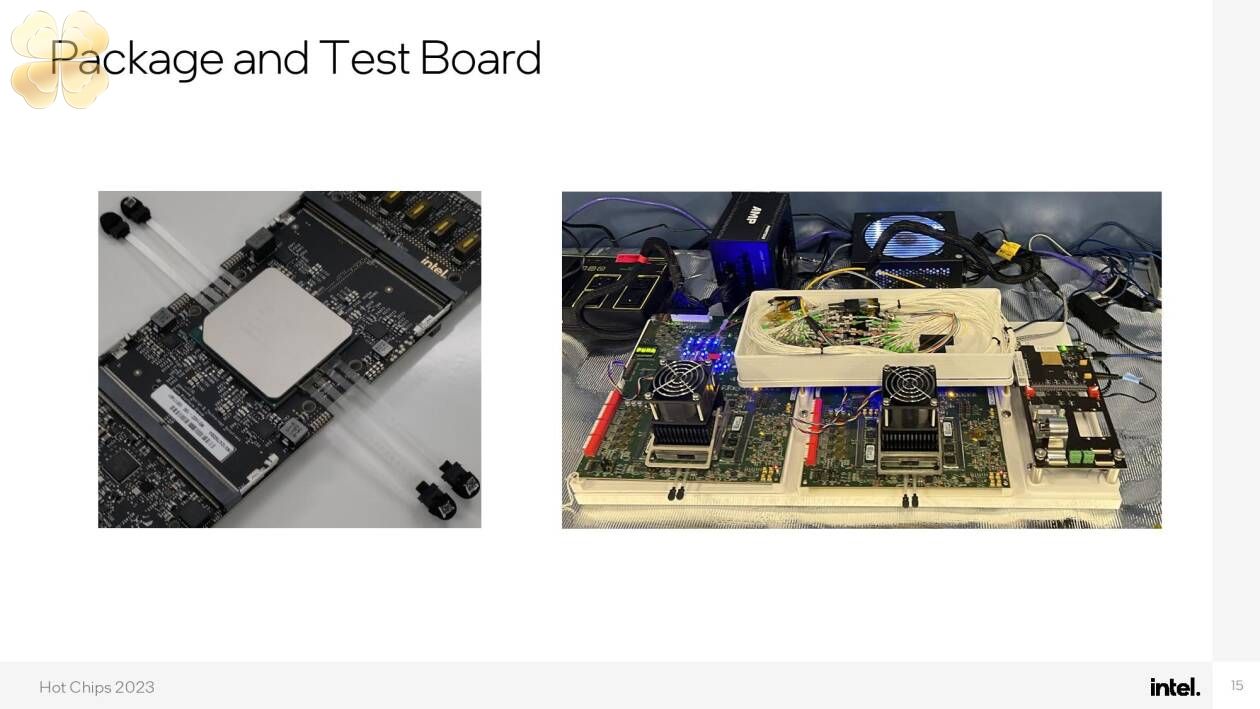

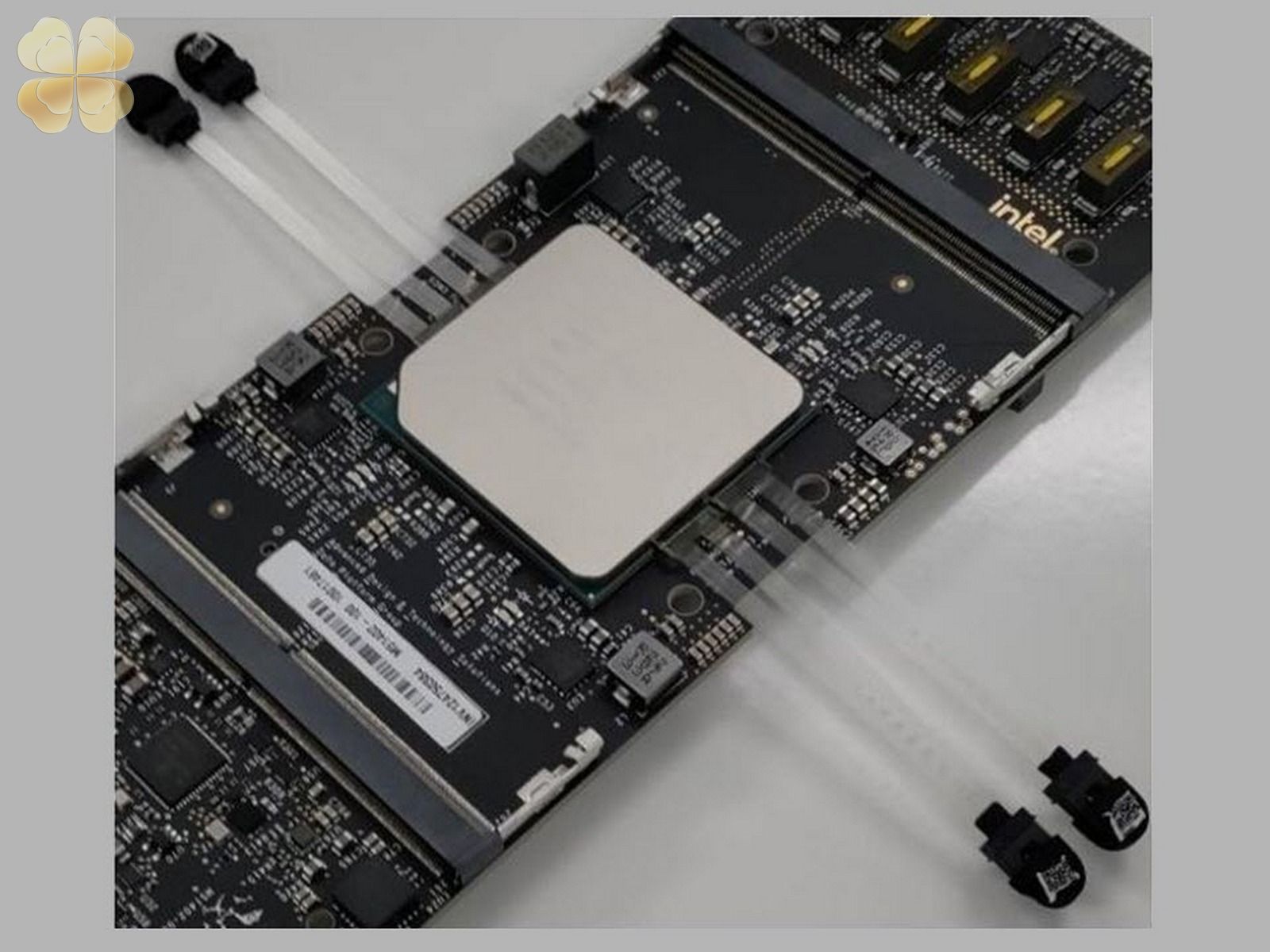

Chip cũng có bốn chiplet I/O quang học tốc độ cao tám kênh, mỗi chiplet ở trên cùng và dưới cùng của die, cầu nối các tín hiệu điện bên trong với các kết nối quang học bên ngoài. Các đơn vị này được kết nối qua bao bì EMIB của Intel và sử dụng giao thức AIB. Chip cũng có kết nối PCIe 4.0 x8 để giao tiếp với hệ thống lưu trữ.

Việc di chuyển lượng dữ liệu đáng kinh ngạc được tạo ra bởi 528 luồng xung quanh die yêu cầu một interconnect được tối ưu hóa, vì vậy Intel đã thiết kế một mesh trên die 2D với 16 router để sắp xếp dữ liệu giữa các lõi, bộ điều khiển bộ nhớ và các kết nối quang học silicon (tám router được tích hợp vào lõi CPU, trong khi sáu router được dành riêng hoàn toàn cho việc di chuyển dữ liệu).

Như bạn có thể thấy trong album trên, các đầu nối quang học được tích hợp vào gói chip và treo ra khỏi các cạnh của chip để liên kết bên ngoài với các chip khác. Chip được kết nối với mạng quang học 'HyperX' bên ngoài cung cấp các kết nối tất cả với tất cả cho các lõi xử lý riêng lẻ. Mạng lưới phi thường này cho phép tối đa hai triệu lõi được kết nối trực tiếp tất cả với tất cả với độ trễ dưới 400ns.

Kết quả cuối cùng rất ấn tượng - chip tiêu thụ chỉ 75W, với 59% ngân sách đó dành cho silicon photonics và 21% dành cho các lõi. Intel tuyên bố rằng hiệu suất được tăng cường của mạng quang học cho phép hiệu scaling

© newsliver.com. All Rights Reserved.