Thiết kế vật lý của các bộ vi xử lý hiện đại thường mất nhiều năm và tốn hàng chục hoặc hàng trăm triệu đô la, tùy thuộc vào độ phức tạp và công nghệ quy trình. Startup bán dẫn Zero ASIC đã công bố một nền tảng cho phép lắp ráp nhanh chóng một hệ thống đa chiplet (SiP) được tùy chỉnh cao từ các chiplet đã biết. Nền tảng ChipMaker được thiết lập để dân chủ hóa phát triển silicon tùy chỉnh.

Việc phát triển một mạch tích hợp dành riêng cho ứng dụng (ASIC) từ ý tưởng đến sản xuất quá lâu và quá tốn kém đối với nhiều công ty khởi nghiệp. Nền tảng ChipMaker của Zero ASIC đơn giản hóa quy trình bằng cách sử dụng các thiết kế dựa trên chiplet, ẩn đi sự phức tạp của thiết kế mạch và cho phép người dùng kiểm tra và sửa đổi nhanh chóng và chính xác các thiết kế tùy chỉnh của họ trước khi đặt hàng các thiết bị vật lý. Tất cả điều này được thực hiện bằng cách sử dụng FPGA đám mây (mảng cổng lập trình trường) để triển khai mã nguồn RTL.

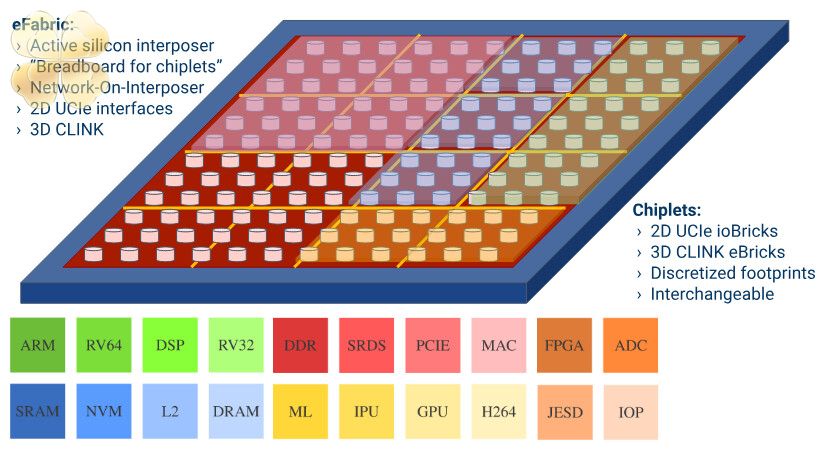

Nền tảng của Zero ASIC dựa trên Efabric, một interposer 3D cho phép giao tiếp giữa các khuôn và Ebrick, một bộ sưu tập các chiplet 3D được chế tạo sẵn với khả năng cắm và chạy. Efabric đóng vai trò như một interposer 3D động với cấu trúc giống như lưới với băng thông phân chia 512 GB/s/mm trên fabric. Interposer 3D tạo điều kiện thuận lợi cho việc tích hợp các đơn vị xử lý bằng cách sử dụng các chiplet Ebrick tương thích được kết nối 3D với băng thông chiplet 3D 128 GB/s/mm2. Nó cũng hỗ trợ kết hợp các chức năng IO ngoài gói thông qua các chiplet IObrick dựa trên UCIe được kết nối 2D với băng thông chiplet 2D 128 GB/s/mm.

Hiện tại, Zero ASIC có một danh mục vừa phải gồm các chiplet Ebrick 2 mm^2, bao gồm CPU dual-issue hỗ trợ Linux lõi tứ RISC-V, FPGA nhúng 5 nghìn LUT, SRAM 3 MB và bộ tăng tốc ML (tera-ops mỗi giây học máy) 3 TOPS. Các chiplet này đang được sử dụng để chứng minh khả năng của nền tảng tại Trung tâm Hội nghị thượng đỉnh nền tảng máy tính mở / Nền kinh tế chiplet mở vào ngày 17-19 tháng 10, tại San Jose, California. Zero ASIC kỳ vọng danh mục các chiplet Ebrick sẽ mở rộng đáng kể theo thời gian. Điều này sẽ cho phép nền tảng ChipMaker trở nên khả thi hơn bao giờ hết, mặc dù họ không tiết lộ cách thức đạt được điều này.

"Mạch tích hợp dành riêng cho ứng dụng (ASIC) tùy chỉnh cung cấp lợi thế về chi phí và năng lượng gấp 10-100 lần so với các thiết bị thương mại ngoài kệ (COTS), nhưng chi phí phát triển khổng lồ khiến ASIC không khả thi đối với hầu hết các ứng dụng", Andreas Olofsson, Giám đốc điều hành và người sáng lập của Zero ASIC cho biết. "Để xây dựng làn sóng tiếp theo của các thiết bị silicon thay đổi thế giới, chúng ta cần giảm rào cản đối với ASIC theo cấp số nhân. Sứ mệnh của chúng tôi tại Zero ASIC là làm cho việc đặt hàng ASIC dễ dàng như đặt hàng các bộ phận danh mục từ nhà phân phối điện tử."

Nghe có vẻ thú vị. Liệu nó có thực sự hoạt động và đạt được sức hút hay không vẫn còn được xem xét.

© newsliver.com. All Rights Reserved.