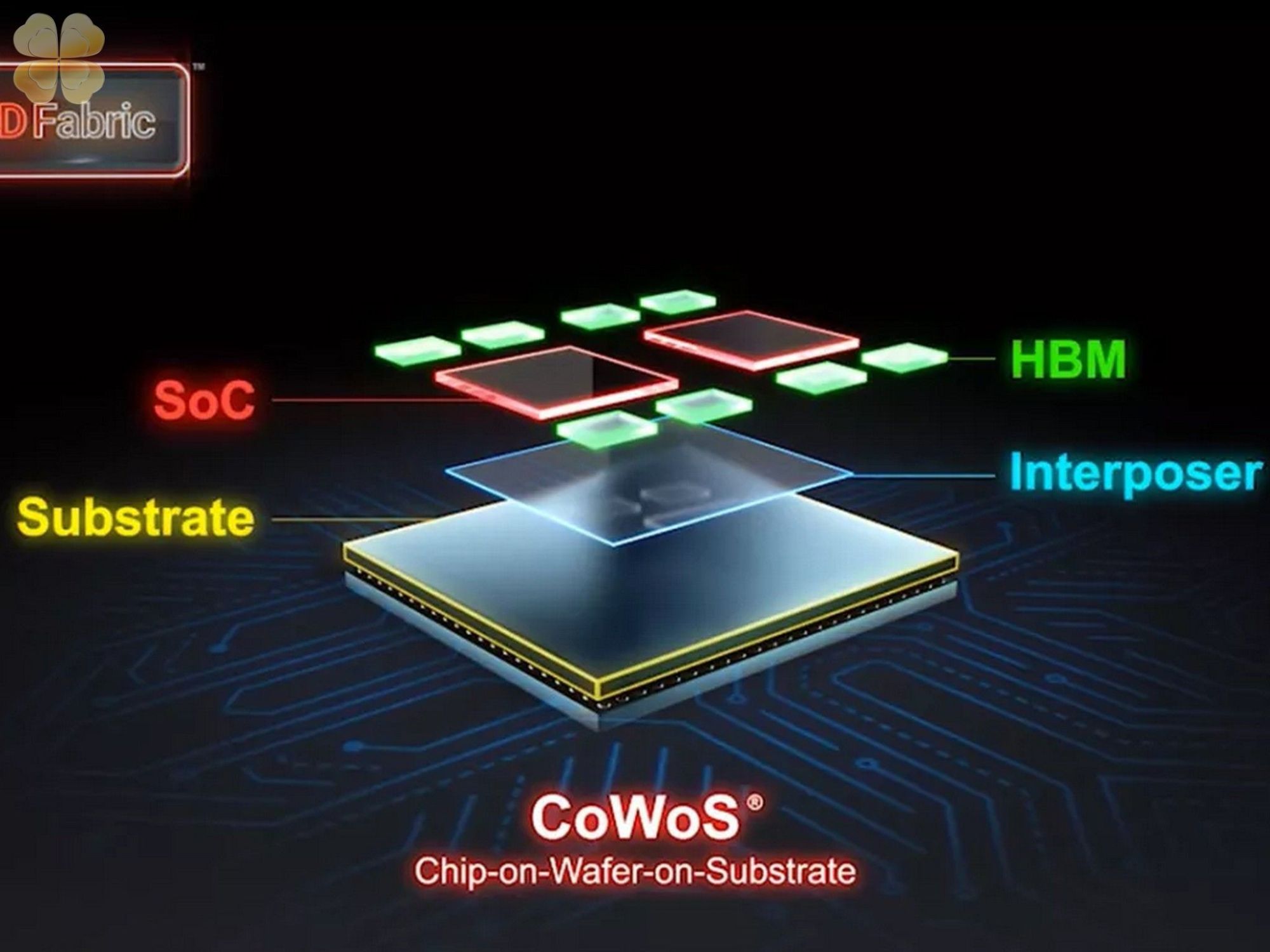

Chủ tịch TSMC thừa nhận rằng nguồn cung chip GPU tính toán cho các ứng dụng trí tuệ nhân tạo (AI) và điện toán hiệu suất cao (HPC) hiện đang thiếu do hạn chế về năng lực đóng gói chip-on-wafer-on-substrate (CoWoS). Tình trạng thiếu hụt này dự kiến sẽ tiếp tục trong khoảng 18 tháng do nhu cầu ngày càng tăng đối với các ứng dụng AI tổng hợp và tốc độ mở rộng năng lực CoWoS của TSMC tương đối chậm.

"Không phải thiếu chip AI, mà là thiếu năng lực CoWoS của chúng tôi," Mark Liu, chủ tịch TSMC, cho biết trong cuộc trò chuyện với Nikkei tại Semicon Taiwan. "Hiện tại, chúng tôi không thể đáp ứng 100% nhu cầu của khách hàng, nhưng chúng tôi cố gắng hỗ trợ khoảng 80%. Chúng tôi nghĩ đây là hiện tượng tạm thời. Sau khi mở rộng [năng lực đóng gói chip tiên tiến], nó sẽ được giải quyết trong một năm rưỡi."

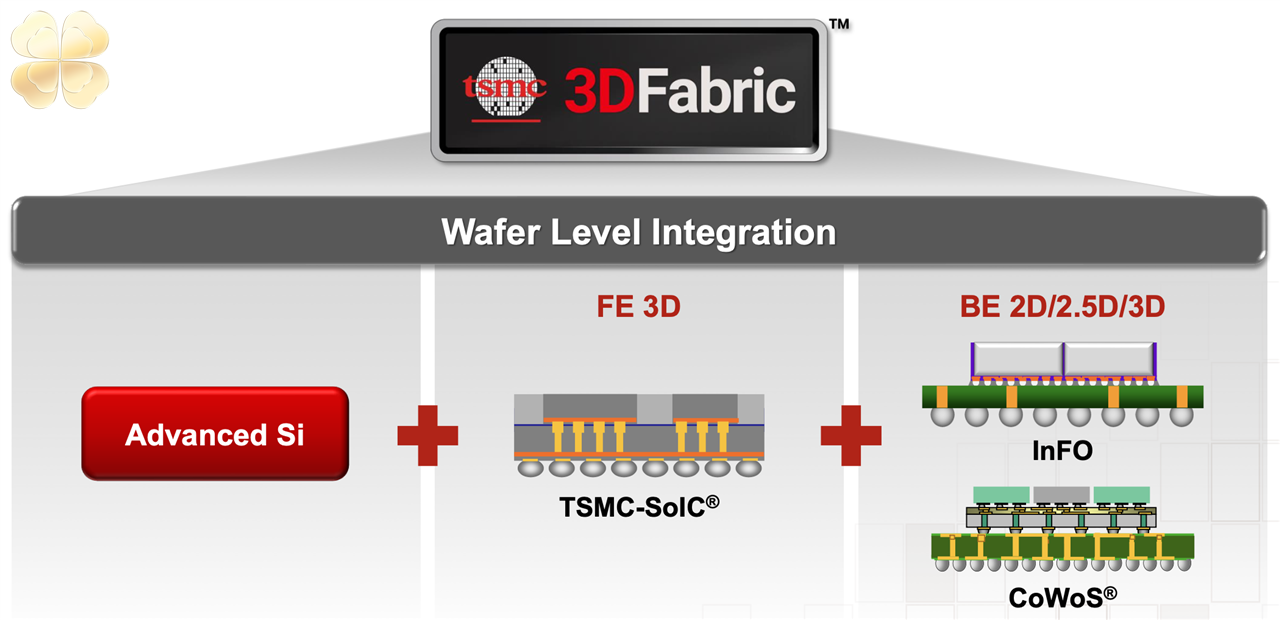

TSMC là nhà sản xuất chip AI lớn nhất, bao gồm cả chip GPU tính toán A100 và H100 của Nvidia, là thành phần quan trọng của các công cụ AI như ChatGPT và chủ yếu được sử dụng trong các trung tâm dữ liệu AI. Các chip này, giống như các giải pháp của các nhà sản xuất khác như AMD, AWS và Google, đều sử dụng bộ nhớ HBM (thiết yếu cho băng thông cao và hoạt động bình thường của các mô hình ngôn ngữ AI lớn) và đóng gói CoWoS, điều này gây thêm áp lực cho các cơ sở đóng gói tiên tiến của TSMC.

Liu cho biết nhu cầu về CoWoS đã tăng đột biến vào đầu năm nay, tăng gấp ba lần so với cùng kỳ năm trước, dẫn đến tình trạng thiếu hụt nguồn cung hiện tại. TSMC nhận thấy rằng nhu cầu về các dịch vụ AI tổng hợp đang tăng lên và nhu cầu về phần cứng phù hợp cũng tăng lên, vì vậy họ đang tăng tốc mở rộng năng lực CoWoS để đáp ứng nhu cầu về chip GPU tính toán cũng như các bộ tăng tốc và bộ xử lý AI chuyên dụng.

Hiện tại, công ty đang lắp đặt thêm các công cụ cho CoWoS tại các cơ sở đóng gói tiên tiến hiện có, nhưng điều này cần thời gian và công ty dự kiến năng lực CoWoS của họ sẽ tăng gấp đôi vào cuối năm 2024.

Ngoài ra, TSMC gần đây đã công bố kế hoạch đầu tư 2,9 tỷ USD vào một cơ sở mới chuyên về đóng gói chip tiên tiến. Cơ sở này, nằm gần Miaoli, Đài Loan, là minh chứng cho cam kết của công ty trong việc giải quyết nhu cầu về đóng gói chip tiên tiến từ tất cả các ngành và công ty đã công nhận tầm quan trọng của đóng gói chip tiên tiến trong ngành bán dẫn trong tương lai.

Sự tập trung vào đóng gói chip tiên tiến không chỉ dành riêng cho TSMC; các gã khổng lồ khác trong ngành như Intel và Samsung cũng đang ưu tiên nó, với Intel đặt mục tiêu tăng gấp bốn lần công suất đóng gói chip hàng đầu của mình vào năm 2025. Các công ty gia công lắp ráp và thử nghiệm bán dẫn (OSAT) truyền thống như ASE và Amkor cũng có các công nghệ tương tự như CoWoS, nhưng họ vẫn phải xây dựng năng lực cho chúng tương đương với TSMC, Intel và Samsung.

© newsliver.com. All Rights Reserved.