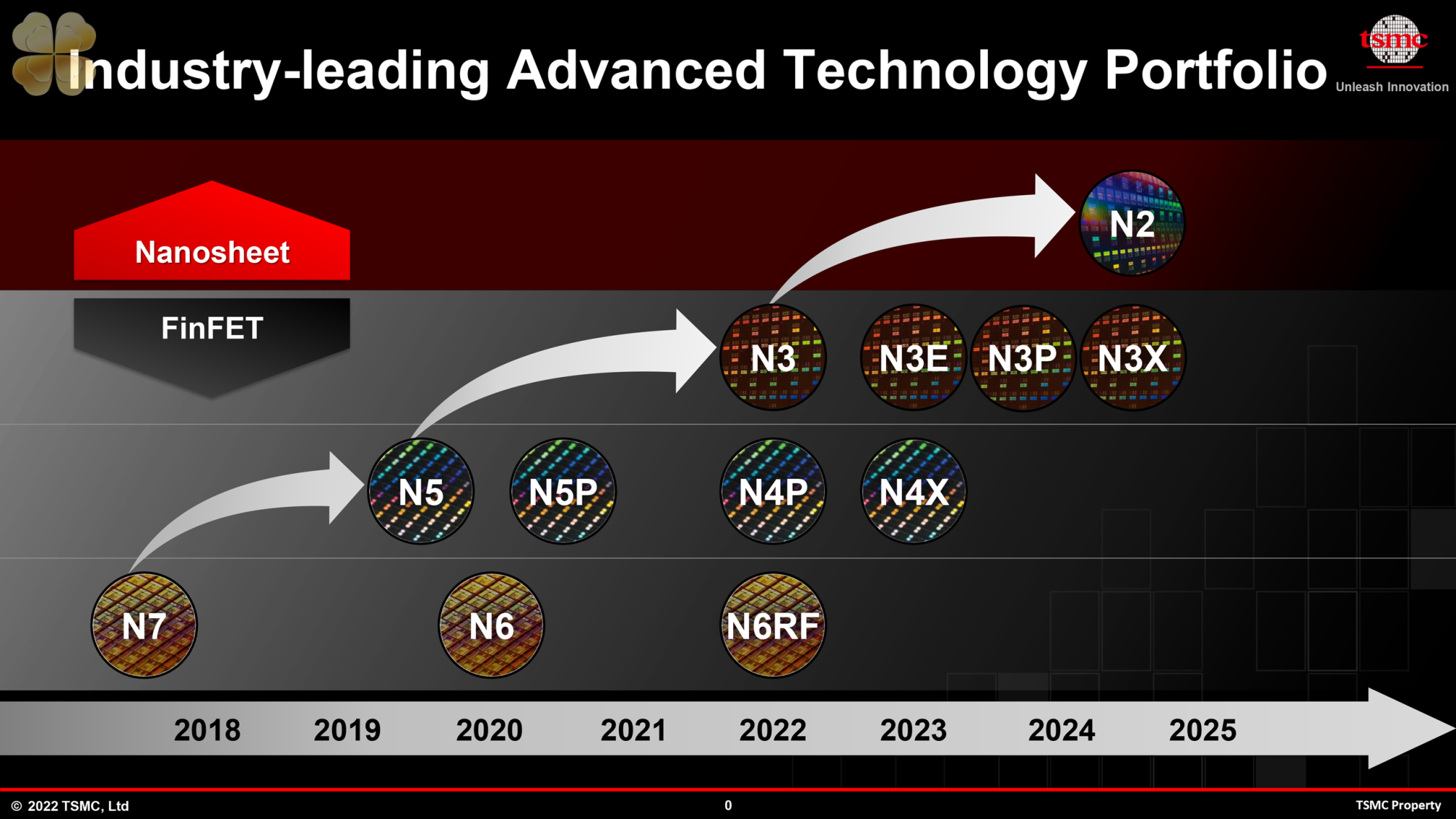

TSMC vừa công bố chi tiết về quy trình sản xuất N2 (2nm) đột phá tại hội nghị IEEE International Electron Devices Meeting (IEDM)! Công nghệ này hứa hẹn giảm tiêu thụ điện năng từ 24% đến 35% hoặc tăng hiệu năng 15% ở cùng điện áp, cùng với mật độ bóng bán dẫn cao hơn 115% so với thế hệ 3nm trước đó. Điểm nổi bật của N2: * Transistor GAA Nanosheet: Thiết kế tiên tiến cho phép điều chỉnh chiều rộng kênh, cân bằng hiệu năng và tiết kiệm năng lượng tối ưu. Kết hợp với công nghệ Nanoflex DTCO, N2 cho phép thiết kế các tế bào ngắn, nhỏ gọn, tiết kiệm năng lượng hoặc các tế bào cao hiệu suất tối đa. * 6 mức ngưỡng điện áp (6-VT): Tối ưu hóa hiệu quả năng lượng với phạm vi 200mV, nhờ tích hợp lưỡng cực thế hệ thứ ba. Tăng tốc độ I/CV lên khoảng 70% (cho transistor N-type) và 110% (cho transistor P-type). * Hiệu suất vượt trội ở điện áp thấp: N2 mang lại hiệu năng/watt tốt hơn đáng kể so với FinFET, đặc biệt ở điện áp 0.5V-0.6V, tăng tốc độ xung nhịp khoảng 20% và giảm tiêu thụ điện năng chờ lên đến 75%. * Mật độ SRAM kỷ lục: Công nghệ N2 đạt mật độ SRAM 2nm lên đến 38MB/mm², tiết kiệm năng lượng đáng kể nhờ độ biến thiên điện áp ngưỡng (VT-sigma) thấp. Điện áp hoạt động tối thiểu (Vmin) giảm 20-35mV so với thiết kế dựa trên FinFET. * Cải tiến đường dẫn: Sử dụng dây dẫn Tungsten không cần lớp ngăn cách, giảm điện trở 20%, tăng tần số dao động vòng lên 6.2%. Quá trình sản xuất M1 đơn giản hơn, tiết kiệm mặt nạ EUV và giảm điện dung tế bào chuẩn gần 10%. * Tích hợp 3D: Hỗ trợ tùy chọn Cu RDL với lớp phủ phẳng và TSV, tối ưu cho việc xếp chồng 3D, mở ra khả năng ứng dụng rộng rãi trong AI, HPC và cả thiết kế di động. TSMC dự kiến bắt đầu sản xuất hàng loạt N2 vào cuối năm 2025, hứa hẹn một cuộc cách mạng trong ngành công nghiệp bán dẫn!

© newsliver.com. All Rights Reserved.