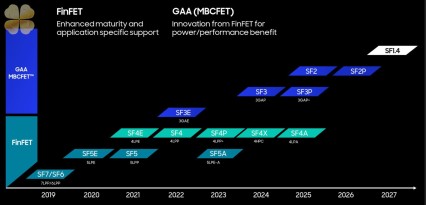

Intel Ra Mắt Trang Web Đặc Biệt Về Công Nghệ 18A

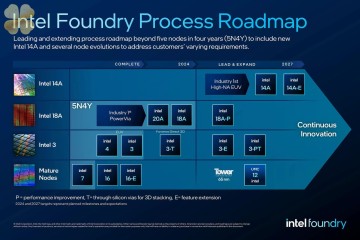

Intel vừa tung ra một trang web đặc biệt, hoàn toàn dành riêng cho công nghệ sản xuất chip 18A, hay còn gọi là tiến trình 1.8 nanomet. Đây là một động thái khá bất ngờ từ Intel, bởi vì trang web này chủ yếu tập trung vào những cột mốc quan trọng mà công ty đã công bố trước đó. Tuy nhiên, trong bối cảnh hiện tại, khi Intel đang chịu áp lực lớn từ các nhà đầu tư, giới quan sát thị trường, khách hàng, đối thủ cạnh tranh, và thậm chí cả giới chính trị, thì việc ra mắt một trang web như vậy có thể là một ý tưởng không tồi.